# **AEROSPACE STANDARD**

AS4710

1993-05 Issued Reaffirmed 2006-07

PI-BUS

**RATIONALE**

This document has been reaffirmed to comply with the SAE 5-year Review policy.

**FOREWORD**

(This foreword is not part of the SAE requirements for 4710, SAE AS Pi-Bus Standard)

As part of the VHSIC Phase 2 program, IBM, TRW, and Honeywell developed a specification for a 16 or 32-bit parallel backplane communication bus. This specification was the VHSIC Phase 2, Interoperability Standard PI-Bus Specification 2.2. The Joint Integrated Avionics Working Group (JIAWG) adopted the Pi-Bus as its "standard" backplane communications bus. However, by examining the various Pi-Bus implementations occurring during the initial phases of JIAWG, it was determined that the VHSIC Pi-Bus Specification needed some clarification to better support interoperability and some modifications to support JIAWG requirements. The JIAWG formed a Pi-Bus Working Group whose goal was to develop a JIAWG Pi-Bus specifications by enhancing/modifying the VHSIC Pi-Bus Specification. The membership of the JIAWG Pi-Bus Working Group happened to also be a subset of the SAE AS-2C1 Pi-Bus Working Group. Since the VHSIC Pi-Bus Specification was not being maintained and since the Pi-Bus had applicability beyond JIAWG, the two working groups met in concert with a goal of first creating a JIAWG Pi-Bus Specification and then transitioning this specification to become an SAE standard. This standard represents over 4 years of effort by a number of dedicated individuals to achieve this goal.

This standard was prepared by the SAE AS-2C1 Pi-Bus Working Group. There were in excess of 25 individuals who supported this effort over the 4 years of its development. At the time the standard was approved, the active membership of the working group was as follows:

Chuck Roark, Chairman Fred Jackson, Vice Chairman Paul Bowen, Secretary Dave Dzatko John Libby Dennis Kalajainen Tracy Markie Denise Kelley-Jones Tom McDermott Sheila Kline

SAE Technical Standards Board Rules provide that: "This report is published by SAE to advance the state of technical and engineering sciences. The use of this report is entirely voluntary, and its applicability and suitability for any particular use, including any patent infringement arising therefrom, is the sole responsibility of the user."

SAE reviews each technical report at least every five years at which time it may be reaffirmed, revised, or cancelled. SAE invites your written comments and suggestions. Copyright © 2006 SAE International

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of SAE.

TO PLACE A DOCUMENT ORDER: 877-606-7323 (inside USA and Canada) Tel:

Tel: 724-776-4970 (outside USA) Fax: 724-776-0790

Email: CustomerService@sae.org

SAE WEB ADDRESS: http://www.sae.org

# TABLE OF CONTENTS

| 1.    | SCOPE                                                         | 7   |

|-------|---------------------------------------------------------------|-----|

| 1.1   | Purpose                                                       | 7   |

| 1.2   | Field of Application                                          | 7   |

| 1.3   | Classification                                                | 7   |

| 1.3.1 | 16 ED Mode                                                    | 8   |

| 1.3.2 | 32 EC Nonmixed Mode                                           |     |

|       | 32 EC Mixed Mode                                              |     |

|       |                                                               |     |

| 2.    | REFERENCES                                                    | 8   |

|       |                                                               |     |

| 2.1   | Applicable Documents  Military Documents                      | 8   |

| 2.1.1 |                                                               |     |

| 2.2   | Definitions                                                   | R   |

| 2.2.1 | Item Definitions  Term Definitions                            | 9   |

| 2.2.2 | Term Definitions                                              | 10  |

| 2.3   | Abbreviations and Acronyms                                    | 12  |

|       | . Q                                                           | -   |

| 3.    | PHYSICAL LAYER                                                | 13  |

| · .   | Abbreviations and Acronyms  PHYSICAL LAYER  Introduction      | . • |

| 3.1   | Introduction                                                  | 12  |

| 3.2   | Line Definitions  Nomenclature  Bused Signal Lines  Bus Clock | 13  |

| 3.2.1 | Nomenclature                                                  | 13  |

| 322   | Bused Signal Lines                                            | 14  |

| 323   | Bus Clock                                                     | 20  |

| 3 2 4 | Module Identification (MID)                                   | 20  |

| 325   | 32-Bit FC/Dual 16-Bit FD Interoperability                     | 20  |

| 326   | 32-Bit EC/Dual 16-Bit ED Interoperability                     | 20  |

| 3.3   | Electrical Requirements                                       | 22  |

| 3.3.1 | Backplane Requirements                                        | 22  |

|       | Module Requirements                                           | 24  |

| 0.0.2 | Woodio (Coqui official)                                       |     |

| 4.    | Data link LAYER                                               | 28  |

| ••    |                                                               |     |

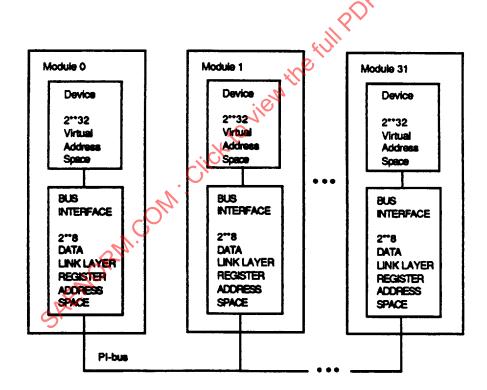

| 4.1   | Introduction                                                  | 28  |

| 4.2   | General Requirements                                          | 28  |

| 4.2.1 | Introduction                                                  |     |

|       | Protocol State Transitions                                    |     |

|       | Generic Message                                               |     |

| 4.3   | Detailed Requirements                                         |     |

| 4.3.1 | Introduction                                                  |     |

|       | Bus State Definitions                                         |     |

|       | Bus Mastership                                                |     |

|       | Message Sequences                                             |     |

|       | Exception Sequences                                           |     |

|       | Wait                                                          |     |

|       | Data Link and System Time Facilities                          |     |

|       | Initialization                                                |     |

|       | Error Detection, Recovery and Diagnostics                     |     |

| 1.0.0 | Error Dotoonori, recovery and Diagnostico                     | .00 |

# LIST OF TABLES

| TABLE 1  | Bus Configuration Types                                                                      | 7  |

|----------|----------------------------------------------------------------------------------------------|----|

| TABLE 2  | Pi-Bus Signal Line Requirements By Type, Class and Mode                                      | 15 |

| TABLE 3  | Pi-Bus Cycle Types and Valid Symbols                                                         | 17 |

| TABLE 4  | Cycle Type Symbol Interpretation                                                             | 18 |

| TABLE 5  | Acknowledge Line Set Valid Symbols                                                           |    |

| TABLE 6  | Pi-Bus Signal Pairing                                                                        | 21 |

| TABLE 7  | Signal Partitioning                                                                          | 21 |

| TABLE 8  | Pi-Bus Communications Sequences                                                              | 29 |

| TABLE 9  | Pi-Bus Protocol States                                                                       | 31 |

| TABLE 10 | Pi-Bus Protocol States                                                                       | 33 |

| TABLE 11 | Mixed Mode Data Format Matrix                                                                | 38 |

| TABLE 12 | Message Type CodesAT (Access Type) Code Assignments                                          | 39 |

| TABLE 13 | AT (Access Type) Code Assignments                                                            | 40 |

| TABLE 14 | Multiple Slave Acknowledge Symbol Formats (Four Words)                                       | 48 |

| TABLE 15 | Multiple Slave Acknowledge Symbols (Four Words) Data Check Line Formats (Used                |    |

|          | only for Class EC)                                                                           | 48 |

| TABLE 16 | only for Class EC)  Bus State Definitions  Vie Sequence  Module Vie Code Format - Data Lines | 50 |

| TABLE 17 | Vie Sequence                                                                                 | 54 |

| TABLE 18 | Module Vie Code Format - Data Lines                                                          | 54 |

| TABLE 19 | Module Vie Code Format - Data Check Lines                                                    | 55 |

| TABLE 20 | Parameter Write Sequence - Type 16 ED Single Slave                                           | 57 |

| TABLE 21 | Parameter Write Sequence - Type 16 ED Multiple Slave                                         | 57 |

| TABLE 22 | Parameter Write Sequence - Type 32 EQSingle Slave                                            | 58 |

| TABLE 23 | Parameter Write Sequence - Type 32 EC Multiple Slave                                         |    |

| TABLE 24 | Block Message - SH Sequence - Type 16 ED Single Slave                                        | 62 |

| TABLE 25 | Block Message - SH Sequence - Type 16 ED Multiple Slave                                      | 62 |

| TABLE 26 | Block Message - SH Sequence - Type 32 EC Single Slave                                        | 63 |

| TABLE 27 | Block Message - SH Sequence - Type 32 EC Multiple Slave                                      | 64 |

| TABLE 28 | Block Message - EH Sequence - Type 16 ED Single Slave                                        | 69 |

| TABLE 29 | Block Message - EH Sequence - Type 16 ED Multiple Slave                                      | 70 |

| TABLE 30 | Block Message - EH Sequence - Type 32 EC Single Slave                                        | 71 |

| TABLE 31 | Block Message EH Sequence - Type 32 EC Multiple Slave                                        | 72 |

| TABLE 32 | Bus Interface Message Sequence - Type 16 ED and Type 32 EC Single Slave                      | 76 |

| TABLE 33 | Bus Interface Message Sequence - Type 16 ED and Type 32 EC                                   |    |

|          | Multiple Slave                                                                               | 76 |

| TABLE 34 | Datagram Message (Non-Acknowledged) - SH Sequence Type 16 ED                                 |    |

|          | Multiple Slave                                                                               | 81 |

| TABLE 35 | Datagram Message (Non-Acknowledged) - SH Sequence Type 32 EC                                 |    |

|          | Multiple Slave                                                                               | 81 |

| TABLE 36 | Acknowledged Datagram Message - SH Sequence Type 16 ED                                       |    |

|          | Multiple Slave                                                                               | 82 |

| TABLE 37 | Acknowledged Datagram Message - SH Sequence Type 32 EC                                       |    |

|          | Multiple Slave                                                                               | 83 |

| TABLE 38 | Datagram Message (Non-Acknowledged) - EH Sequence Type 16 ED                                 |    |

|          | Multiple Slave                                                                               | 86 |

| TABLE 39 | Datagram Message (Non-Acknowledged) - EH Sequence                                            | 86 |

| TABLE 40 | Acknowledged Datagram Message - EH Sequence Type 16 ED                                       |    |

|          | Multiple Slave                                                                               | 87 |

|          |                                                                                              |    |

# LIST OF TABLES (Continued)

| TABLE 41 | Acknowledged Datagram Message - EH Sequence Type 32 EC                                                       |     |

|----------|--------------------------------------------------------------------------------------------------------------|-----|

|          | Multiple Slave                                                                                               | 88  |

| TABLE 42 | Suspend - Short Data Sequence - Type 16 ED Single Slave                                                      | 91  |

| TABLE 43 | Suspend - Short Data Sequence - Type 32 EC Single Slave                                                      |     |

| TABLE 44 | Suspend - Extended Data Sequence - Type 16 ED Single Slave                                                   | 92  |

| TABLE 45 | Suspend - Extended Data Sequence - Type 32 EC Single Slave                                                   |     |

| TABLE 46 | Suspend - Type 16 ED Block Message Multiple Slave                                                            | 94  |

| TABLE 47 | Suspend - Type 32 EC Block Message Multiple Slave                                                            | 94  |

| TABLE 48 | Suspend - Type 16 ED Non-Acknowledge Datagram Multiple Slave                                                 | 95  |

| TABLE 49 | Suspend - Type 32 EC Non-Acknowledge Datagram Multiple Slave                                                 |     |

| TABLE 50 | Suspend - Type 16 ED Acknowledged Datagram Multiple Slave                                                    | 96  |

| TABLE 51 | Suspend - Type 32 EC Acknowledged Datagram Multiple Slave                                                    | 96  |

| TABLE 52 | Abort Sequence                                                                                               | 98  |

| TABLE 53 | Data Link Address Space                                                                                      | 100 |

| TABLE 54 | Interpretation for Uncorrectable Invalid Symbol                                                              | 106 |

| TABLE 55 | Abort Sequence                                                                                               | 107 |

| TABLE 56 | Cycle Type Deviation Response Definitions                                                                    | 107 |

| TABLE 57 | Sequence Error Response                                                                                      | 108 |

| TABLE 58 | Semantic Errors                                                                                              | 109 |

| TABLE 59 | Acknowledge Semantic Error                                                                                   | 110 |

|          | Cycle Type Deviation Response Definitions Sequence Error Response Semantic Errors Acknowledge Semantic Error |     |

|          |                                                                                                              |     |

| LIST OF ERROR TABLE | S |

|---------------------|---|

|                     |   |

| Error Table 1  | Message Type Format Errors (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 114 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Error Table 2  | Block Message Format and Device Errors (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 115 |

| Error Table 2A | Block Message Header Format and Device Errors (Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|                | Operation for Label Block Messages)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 116 |

| Error Table 3  | Acknowledged Datagram Message (AT = 4-7) Format and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|                | Device Error (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 117 |

| Error Table 3A | Non-Acknowledged Datagram Message (AT = 0-3) Format and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|                | Device Error (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 118 |

| Error Table 4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Error Table 5  | Parameter Write Message Format Errors (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 119 |

| Error Table 6  | Reserved Message Type Format Errors (MT=0, 2, 10) (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 119 |

| Error Table 7  | Vie Sequence Pi-Bus Errors (All Modules)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 120 |

| Error Table 8  | Vie Sequence Pi-Bus Errors (All Modules)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121 |

| Error Table 9  | H1 Through HAn Pi-Bus Errors (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 122 |

| Error Table 10 | DO Through DAn Pi-Bus Errors (Slave Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Error Table 11 | HO Through HZ Errors (Master Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 124 |

| Error Table 12 | HAO Through HAn Errors or HAO Through HAn+2 For Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|                | Writes (Master Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 125 |

| Error Table 13 | Writes (Master Mode)  DO Through DZ Errors (Master Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 126 |

| Error Table 14 | DAO Thuanah DAn O Curara (Mantar Manta)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 127 |

| Error Table 15 | Nontransfer Cycles From HAn+3 through HO Errors, Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                | Write (Master Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 128 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                | and the second s |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                | $\cdot$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|                | $\mathcal{A}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |